- HOME

- 半導体パッケージ基板製造プロセス

IC Package

Substrate

Manufacturing Process半導体パッケージ基板製造プロセス

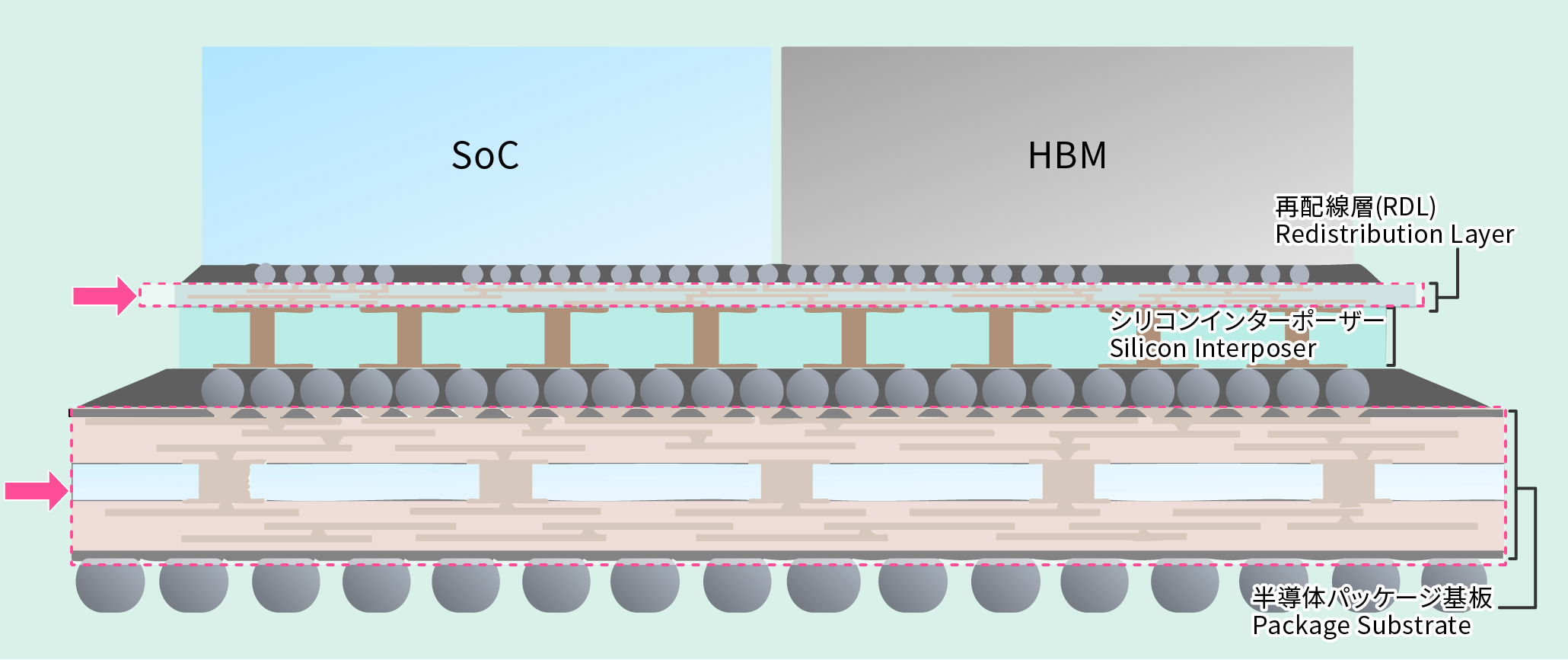

半導体の高性能化をコスト低減の面から支える技術として、回路を個片化して一つの半導体パッケージに収める「チップレット」が注目を集めています。先端半導体パッケージのチップレット間の接続には主にシリコンインターポーザーが使用されていますが、半導体パッケージの大型化や歩留、コストに課題を抱えています。

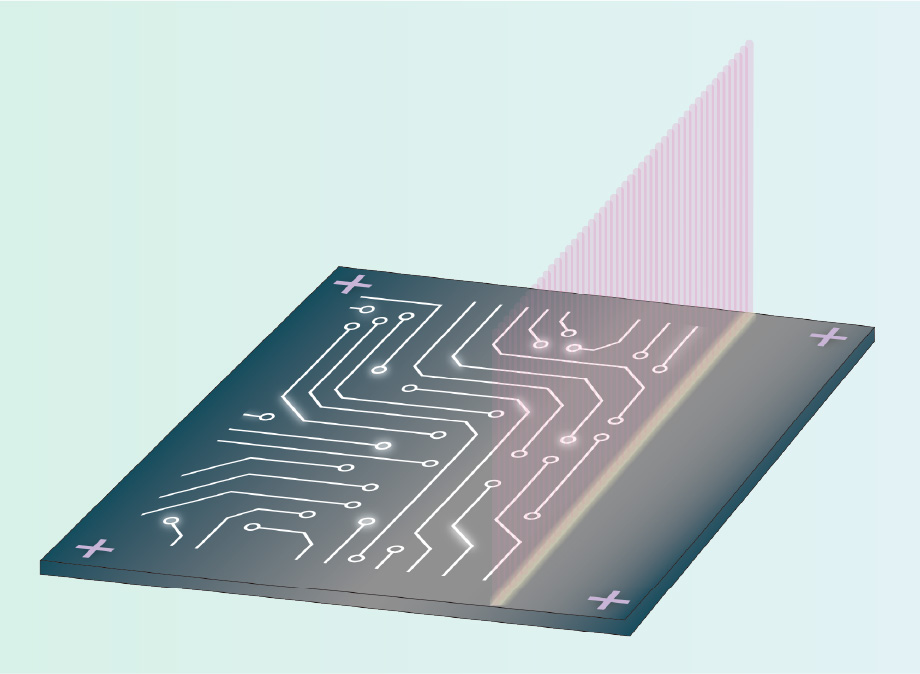

信越化学ではアブレーション加工によって、有機絶縁層に微細な電気回路パターンを掘り込むエキシマレーザー装置を開発しました。これにより、シリコンインターポーザーでしか達成できなかった微細配線や極小ビアを半導体パッケージ基板、再配線層(RDL)、有機インターポーザーなどに形成することができます。

半導体パッケージ基板製造プロセス動画

信越デュアルダマシン法の特長Shin-Etsu Dual Damascene Process Features

信越化学のエキシマレーザー装置を使用することで、半導体前工程で用いられるデュアルダマシン工法を後工程パッケージ基板製造に応用することが可能です。(信越デュアルダマシン法)

SAP(Semi-Additive Process)を代替する埋込配線法

-

信越デュアルダマシン法

レジストを使用せず、エキシマレーザーでビアや配線を加工するため、工程数の削減が可能です。

また、レーザードリルのような1by1の加工ではなく、加工スピードがビア数に依存しないスキャン加工で、テーパーの立ったビアを加工可能です。(レーザードリル代替)

-

従来のSAP+レーザードリルの課題

ドライフィルムレジストを使用するため、ラミネート、露光、現像プロセスが必要です。

また、レーザードリルによる1by1の加工のため、パネル当たりのビア数が増えると、その分加工時間がかかります。

微細かつ高精度な加工

信越独自の光学システムを使用することで、微細かつ高精度な加工が可能です。

-

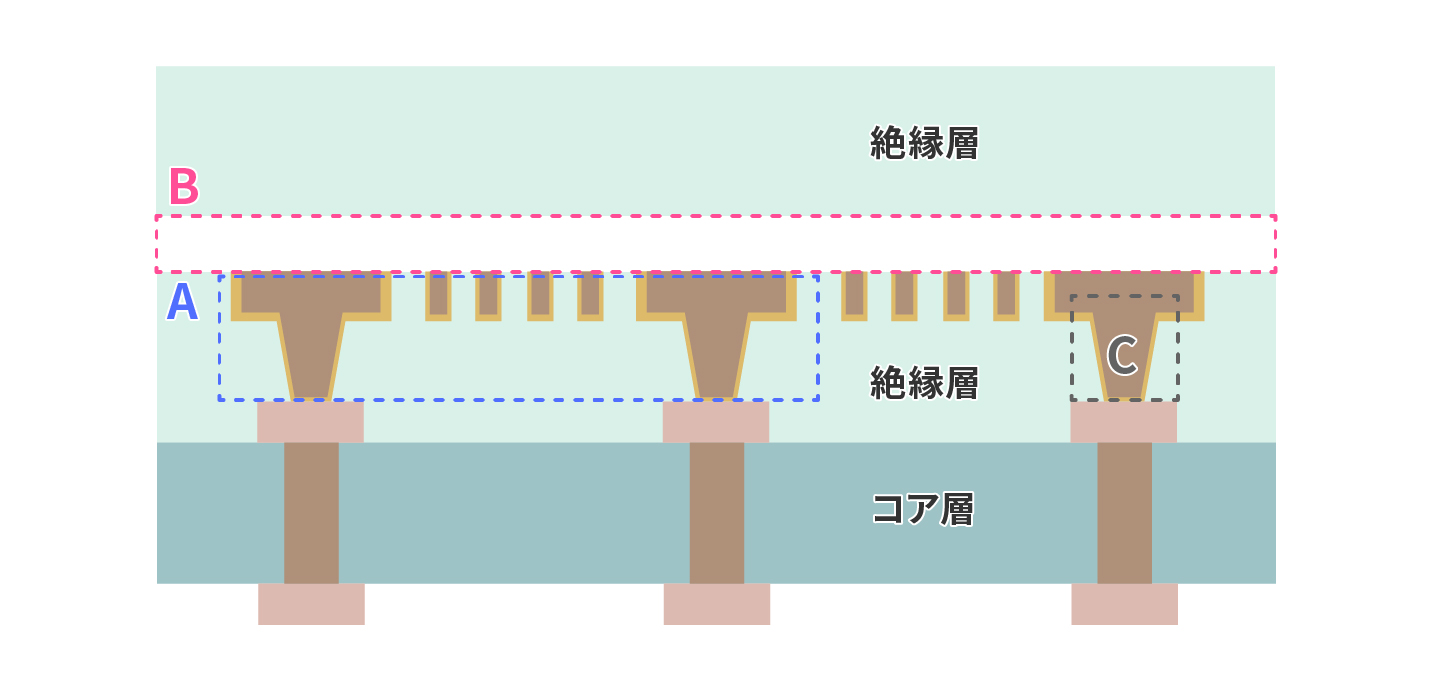

信越デュアルダマシン法

A【高精度なアライメント】

ビアと配線を一台の装置で加工するため、高いアライメント精度を達成することができます。B【埋込配線】

配線が絶縁層に埋め込まれているため、配線折れや有機絶縁膜の充填不足のリスクを低減可能です。C【高テーパー】

エキシマレーザーで加工することで、微細なビアや配線を高テーパーで加工可能です。 -

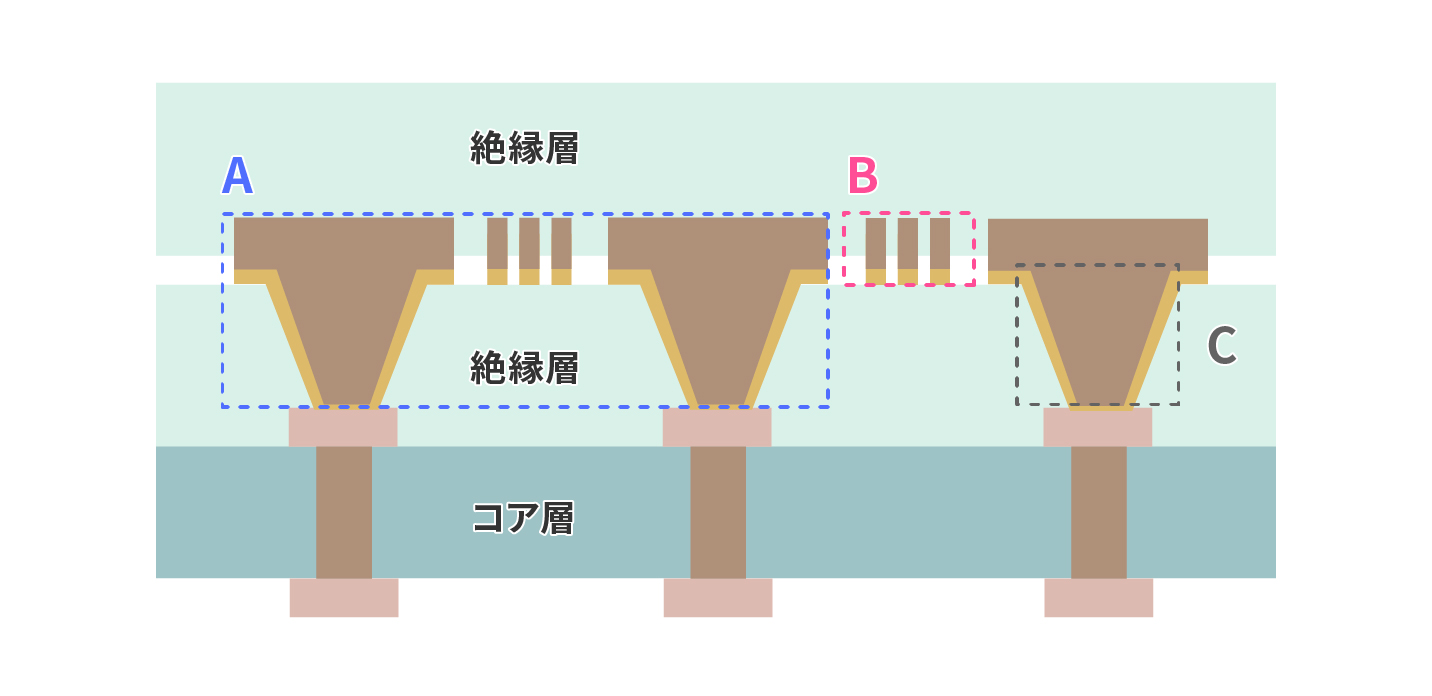

従来のSAP+レーザードリルの課題

A【アライメント】

露光機とレーザードリルのアライメントが必要B【歩留】

ラミネート時の配線折れ・剥離や有機絶縁膜の充填不足リスクが高まるため、微細配線の形成が困難C【レーザードリルの加工精度】

ビアのテーパー、極小化、精度の限界

その他のアドバンテージやアプリケーション

半導体パッケージ基板に限らず、再配線層、有機インターポーザーなど様々な有機絶縁層への対応が可能です。

- 配線の細線化、ビアの小径化によるビルドアップ層の積層数を削減可能

- エキシマレーザー装置1台でレーザードリル複数台分のスループットがあるため、工場のフットプリントを削減可能

- 埋込配線のため、パッケージ基板・再配線層(RDL)の電気的な特性や信頼性の向上が見込まれる